博文

“芯”基建-29:制造!制造!制造!:循迹“台湾之光”,窥探制造奥秘

|

汪炼成 2021/07/30 首发于《材料深一度》 公众号

——制造是基础科学的“千锤万凿出深山”,是关键材料的“一夫当关,万夫莫开”,是大件如EUV小丝如探针尖大小设备“大珠小珠落玉盘”的协奏,是工艺辗转反侧的“如切如磋,如琢如磨”,是制程上下求索的“千淘万漉,吹尽狂沙”。

——制造是化学物理机械控制等基础科学,半导体光刻胶金属等材料,EUV沉浸式光刻薄膜沉积干法刻蚀等装备,互连刻蚀沉积光刻等工艺,和gate-last大马士革等制程,爱恨交织暧昧缠绵长期煎熬不断反馈相促互进最后达成的互融共吐。

——汪炼成

一、制造!制造!制造!

从美国制裁迫使台积电停止为华为生产导致后者的集成153亿个晶体管,首个采用5nm工艺制程5G手机SoC,麒麟系列第13款芯片的麒麟9000成为“绝唱”,到英特尔7nm制程推迟引发的系列换帅、战略调整、先进芯片制程任务外包等危机,及IDM vs Fab+Fabless模式的激烈争论,到帮助中芯国际完成“28nm、14nm、12nm及N+1等制程规模量产,7nm技术开发和风险量产,帮助三星一举超过台积电16nm工艺制程,直接攻克了14nm FinFET技术工艺的前台积电技术狂人梁孟松……

上述种种事例一无例外的说明制造的极端重要性,是半导体行业的最卡脖子技术。没有制造,芯片只能是空中楼阁,纸上谈兵了。

但另一方面,“制造”这个词本身,却似乎有点落伍或 “硬冷”。很多人认为制造不会像相对论等理论那样高深难懂,甚至潜意识里会自信地认为只要给予足够的物力人力,即使最先进的制造技术,他们自己都有可能攻克,即使他们对制造知之甚少。

但事实是,即使台联电和Global Foundry甚至英特尔这样的大玩家,即使成百上千亿美金和无数人力智力的投入,也依然无法攻克芯片先进制程,于是台联电、Global Foundry等早已放弃先进制程研发,而英特尔疲态已显,三星则勉强跟跑。

只有由张忠谋于1987年创立的台积电,在笑傲半导体代工江湖,几乎一骑绝尘。台积电是台湾最赚钱的企业,被称为是“台湾之光”。据报道,“台积电年产能超过1200万片十二英寸晶圆,2020年占有全球57%的市场代工份额,使用281种不同制程技术为数百家客户生产11,617种不同产品。从1994年上市至今,营收年复合成长率达到17.2%,营业净利年复合成长率16.7%,被称作全球唯一连续20年获选道琼永续发展世界指数的组成企业的半导体公司。”

台积电半导体代工神话肯定是战略管理市场技术等因素的综合体现。

但在芯片制造技术上,确实一直好奇,台积电到底有什么独门武器和秘籍呢?

二、芯片制造关键技术探秘

台积电具有深厚的制造实力,从130nm下节点 Cu/Low-k互连,到193nm ArF沉浸式光刻,到力推的Gate-last FinFET,到EUV,再到当前力推的CoWoS,InFO,SoIC的3D封装技术等……

作为行业顶级玩家,其核心技术自然是外人,甚至内部大多数人都很难企及的机密。这里我们将以奠定和进一步巩固台积电代工地位的Cu/Low-k互连和沉浸式光刻技术为案例,尝试从专利,文献等公开资料去窥探一二。

n Cu/Low-k互连技术

随着制程节点缩短,后端制程(BEOL)金属互连的RC 延迟成为限制芯片速度进一步提升的瓶颈。为降低电容,可选取SiOF (k =3.5–3.8), SiCOH (k =2.2–3.2), 或air gap (k~1.0)取代原来的CVD -SiO2(k =4)。

目前用于IC制造的金属是Al,有其优点:Al和二氧化硅有良好的粘附性,和高纯度硅有很低的接触电阻,且容易干法刻蚀。

但其缺点为:Al和硅在577℃下会共熔,容易破坏浅结形成短路,即“Al钉”;内部Al原子容易在电场作用和热作用下扩散,甚至断开,电迁移可靠性低;随着通孔数量增加,Al硅表面的小接触电阻变大,且Al很难沉积在10:1深宽比的通孔中;Al导电性还不够好(Al;2.65 Ωμ-cm)。

为降低电阻,可选金 (Au; 2.214 Ωμ cm), 铜 (Cu; 1.678 Ωμ cm), 和银 (Ag: 1.587 Ωμ cm)等比电阻比Al更低的金属。且Cu且具有更高的电迁移可靠性。Cu/Low-k互连技术因此被青睐。

但Cu用于芯片制造有其固有缺点:Cu与硅的接触电阻很高;Cu容易扩散进入硅中,引起器件性能灾难;无法像Al一样采用干法刻蚀,即等离子体不能与Cu发生反应生成易挥发的副产物;易氧化;接触粘附性不好。

图1(a)Al互连的工艺流程;(b)Cu互连大马士革工艺。

Al互连的工艺流程(图1(a))通常是:Al薄膜沉积,光刻,干法刻蚀留下需要的Al金属,SiO2沉积,抛光SiO2。Cu无法向Al一样采用干法刻蚀,故采用一种不同的所谓“双大马士革”工艺,大致流程为(图1(b)):SiO2沉积,光刻,刻蚀SiO2,电镀Cu,抛光Cu。

进一步,为控制刻蚀深度,且阻止Cu氧化和往Low-k介质扩散,需要刻蚀阻挡层,或者Cu介质层,一般采用SiN(k值为6.8-7.3)或SiCN(k值为4.0-5.0);Low-k介质一般为多孔形态,较为脆弱,且比表面积较大,为了防止Low-k介质在光刻胶打胶或CMP等工艺中受损,在SiCOH Low-k介质上需沉积SiO2帽层;Cu金属复合层则包括包覆层,一般为TaN/Ta,阻止Cu往Low-k介质扩散,Cu种子层,和Cu电镀层(图2)。

其实Cu大马士革同LED金属电极工艺流程思路是一致的,但后者通过电子束蒸发等物理方法沉积金属,且可直接Lift off去除多余金属。由于Cu大马士革工艺是用在130nm下的先进芯片制造,以及Cu材料的特殊性,使两者完全不可同日而语。

图2 Cu双大马士革工艺:SiN/SiCN介质层+ Low-K 层+SiO2帽层,Via刻蚀,Trench 刻蚀,阻挡层TaN/Ta和Cu种子层沉积,Cu电镀,多余Cu CMP去除。

梁孟松等台积电技术员和工程师自主开发了Cu/Low-k互连技术:

低损Low-k介质工艺:CMP-Free和CMP-Less工艺,通过电化学抛光完全或部分取代CMP,可得到纳米级平整Cu表面和〈111〉晶向控制,减小由CMP导致的Low-k介质材料损伤,甚至应力作用下的界面分离(Liang, M. S. 2001, IEDM,TSMC);Plasma 晶圆处理工艺流程优化,防止Plasma直接作用于Low-k介质(Yue, J. T. (2002, June). IEEE 7th International Symposium on Plasma-and Process-Induced Damage (pp. 166-168))。

高深宽比Vias高保形低缺陷无空洞Cu电镀:对Cu电镀液的光亮剂、整平剂、抑制剂等添加剂和电镀参数综合优化,电镀尖峰电流匀化补偿措施和机制,electro-grafting方法制备Cu种子层等(Shue, W. S. 2006 IEEE International Interconnect Technology Conference (pp. 175-177))。

Cu金属结构和工艺优化:无金属包覆层结构,PECVD生长SiC取代常规TaN金属包覆层,RC延迟和电阻分别降低8%和36%,线间漏电则降低3个数量级(Liang, M. S. IEDM, 2002, (pp. 595-598));在ALD TaN上通过electro-grafting直接制作Cu种子层(Liang, M. S., IEDM 2004. (pp. 337-340));选择沉积Co包覆层,抑制Cu表面空位迁移,提高SM(stress-migration)可靠性,而CuSiX的故意形成可提高Cu和包覆层粘附性,但是空位增多会降低SM可靠性。

Cu 金属微观结构和宏观可靠性:Cu晶界缺陷可以抑制空洞沿晶界移动,形成应力诱导空洞和迁移(stress induced void (SIV) formation, Migration)壁垒,从而提高电迁移可靠性(electromigration lifetime)(Liang, M. S., Proceedings of IEEE 2005 International Interconnect Technology Conference, (pp. 102-104);特征尺寸下降时Cu电阻上升,主要由于侧壁和晶界散射。

n 沉浸式光刻技术

沉浸式光刻技术虽然不是由台积电首创,却是由时任台积电技术处长Burn J Lin在ArF 193nm光刻上首先实现并在产业界发扬光大,直至今天仍应用于先进制程的主流光刻技术。

从瑞利公式可确认光刻分辨率。当NA值为极大0.93,k1为极小0.3时,ArF 193nm干式光刻也可达到63nm精度。Double processing在更小k1值为0.15时,甚至可达32nm分辨率。降低k1值可以通过优化设备,OPC(Optical proximity correction),PSM (Phase-shift mask),Off-axis illumination, polarization exposure甚至是computation lithography等手段来实现。然而0.15的极小k1值却使包括掩模版、光源等光刻设备的制造和工艺得实施非常困难,DOF及对版误差(MEF)等均较难控制,产能很受影响。同时又受限于更短波长光源及系统和材料开发,只能从提高NA值想办法。

沉浸式光刻应运而生,即往镜头和光刻胶之间填充高折射率液体。思路很简单,但是实际难题不少。

在晶圆相对镜头高速移动和光照情形下需保持填充液体的温度、流速、厚度等需接近苛刻的均匀,从而使折射率均匀。温度均匀的控制非常关键。

此外,填充液体流动产生流体应力,一定速度下甚至形成涡流,也可能会产生微气泡,微颗粒沉积等。温度和气压变化也使气体溶解度降低,原来溶解的气体部分释放也形成气泡。晶圆边缘曝光不良的光刻胶也容易非正常脱离进入填充液成为污染颗粒。而装载填充液的沉浸头盔(Immersion Hood)也是不容忽视的重要污染源。

气泡和微颗粒如果发生在光刻胶上曝光前,则会跟随光刻流程造成芯片永久“打印缺陷”,曝光后沉积的微颗粒则暂时留在芯片上。

设备产率产量提升等主要是ASML等合作设备厂商负责,台积电主要在降低沉浸式光刻的制程缺陷上攻关(Lin, Burn J. Comptes Rendus Physique 7.8 (2006): 858-874):

曝光后晶圆清洗:最简单直接方法,去除填充液中沉积在晶圆上的颗粒污染物。但是颗粒污染物有些同晶圆强粘附,难以清洗去除。疏水环境可以防止粘附,但却限制了很多光刻胶的使用。一个解决之道是晶圆式全沉浸曝光,即在整个曝光过程中整个晶圆沉浸于填充液中。这样可以避免局部沉浸式曝光频繁注满和排空填充液过程造成的涡流形成和气泡产生等。晶圆式全沉浸曝光设备可能较干式曝光改进较大,且效率产率较低,当然这主要是ASML要解决的问题。

材料表面结构调整和改性:一种方案是在光刻胶上增加一层透明保护膜,防止填充液中的污染颗粒沉积,光刻胶残胶或溶解气体进入填充液。这会增加额外保护膜沉积、剥离等工艺,且可能会对光刻产生影响。比如保护膜沉积的温度、气氛等可能使光刻胶变性,而机械剥离可能损伤光刻胶,湿法剥离可能会蚀刻光刻胶。找到合适的兼容保护膜也并不容易。

台积电提出在通入高折射率曝光填充液之前,先通入带表面活性剂液体,浸润镜头和晶圆及光刻胶,使颗粒污染物等不易被粘附(US 2005/0205108A1)。

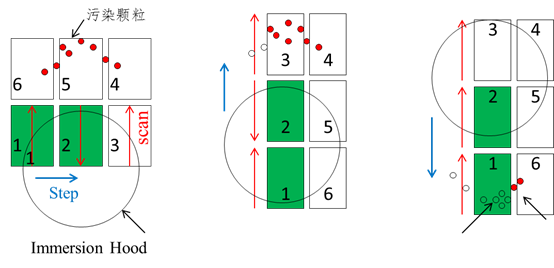

特殊的步进扫描序列:曝光后清洗无法清除“可打印缺陷”, 特殊的步进扫描序列可去除“可打印颗粒污染”。如图3, 常规Routing会使区域5的“可打印污染”曝光后成为永久缺陷。而特殊的Routing 1,至少一半的“可打印污染”被去除,特殊的Routing 2可将大部分去除。但是Routing 2会损失约15%的产率。

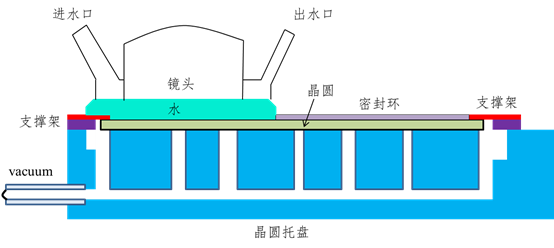

密封环(Seal ring)制程辅助:这是迄今为止台积电提高沉浸式光刻良

率的最行之有效的技术。如图4,密封环由支撑架支撑,后者与晶圆在同一平面。密封环由真空固定防止流体流过晶圆边缘。当沉浸头盔在晶圆边缘时,可消除湍流。污染颗粒不会掉进并积累在晶圆和吸盘之间,并随后回流进入填充液。填充液温度均匀性得到提高和改善。密封环也抑制了晶圆边缘的光刻胶边界剥落,防止其作为颗粒源进入填充液。晶圆Loading和un-loading时,密封环和支撑架可抬升用以取片和放片。

图3特殊的步进扫描序列:(左)常规Routing,(中)特殊Routing 1,(右)特殊Routing 2。

图4用于沉浸式光刻的密封环(Seal ring)辅助结构。

三、先进制造不停步

由上述分析看到,制造其实也并没有那么高深,但却并不简单,需要深刻理解科学原理,调整结构和工艺,改善设备等。

当IC进入 5nm 以后,Cu互连技术也变得吃力,钴或钌取代Cu的技术在被开发。沉浸式光刻则面临偏振曝光,更高折射率填充液及固态高折射填充介质及工艺开发(目前主要是水,折射率为1.43)等更多的困难和挑战。

先进制造的前进脚步没有停止。

目前集成电路芯片制造是基于自上而下路线,或者“减材制造”,在制备更复杂3D堆叠芯片结构将比较困难。前段网络流行如此复杂3D“芯片结构”几乎不可能用现有制造技术实现。

与此相对,自下而上路线是利用原子和分子等较小的构件制造更大的纳米结构,或者“增材制造”,有潜力构建更复杂的微纳结构。东南大学孙立涛教授在前段会议上报告展示了原子级自下而上制备微结构的成果和进展,令人眼前一亮。随着技术推进,原位“生长”出晶体管或芯片,甚至手机耳机等终端产品并非没有可能。

湖南大学段辉高教授在亚10nm微纳制造方面成果颇丰(Chen, Y., Duan, H., Int. J. Extrem. Manuf. 3(2021) 032002 (31p))。

先进制造不局限在“极小极微”,除了极小尺寸的芯片制造,还有极大尺寸空天运载装备铝合金环形构件等。我目前所在高性能复杂制造国家重点实验室,创始和带头人钟掘院士很早就根据国家发展战略目标对制造技术的需求,提出了“极端制造”的概念:在制造尺寸方面极大、极小,在制造环境方面极强、极弱,在制造系统方面实现新效应、新工艺、新装备、新技术,用多种技术极限,构造制造技术与能力极限。

四、制造是科学制程工艺装备的互融共吐

制造不是机械重复式“我亦无他,唯手熟尔”,不是黑箱子式“Try and Test”(从事制造研究很容易陷入上述思维惯性和惰性)。

制造是基础科学的“千锤万凿出深山”,是关键材料的“一夫当关,万夫莫开”,是大件如EUV小丝如探针尖大小设备“大珠小珠落玉盘”的协奏,是工艺辗转反侧的“如切如磋,如琢如磨”,是制程的上下求索“千淘万漉,吹尽狂沙”。

制造不简单,是技术,也是科学。制造是化学物理机械控制等基础科学,半导体光刻胶金属等材料,EUV沉浸式光刻薄膜沉积干法刻蚀等装备,互连刻蚀沉积光刻等工艺,Gate-last FinFET大马士革等制程,爱恨交织暧昧缠绵循环往复长期煎熬不断反馈相促互进最后达成的互融共吐。

在提倡硬科技实产业的当下,包括先进制造,智能制造的制造科学技术和产业将更被重视和发展。

https://m.sciencenet.cn/blog-3362936-1297627.html

上一篇:“芯”基建-28: Micro-LED:未来显示“终极”之探

下一篇:“芯”基建-30:多束并行电子束直写:To be or not to be?